# 20-bit Sigma Delta ADC

The SDADC20 is a 20-bit analog to digital converter implemented as a Sigma Delta architecture. The ADC has programmable analog and digital gain settings. Analog gains of 1x or 2x are selected by an analog gain stage before the data converter. Digital gains of 1x, 2x, 4x, 8x, 16x, 32x, 64x and 128x are selected after the digital decimation filter. The ADC supports offset and gain calibration. The calibration routing calibrates the input voltage standard to a digital full scale output code. The offset and gain calibration results are stored in on chip registers. The offset and gain calibration results can be overwritten during normal operation. Programmability of the ADC's decimation filter, digital gain and analog gain allow for tuning of the converter's data rate, noise and resolution for different modes of operation. The ADC can operate in single-end or differential mode. The digital output formats for single-ended and differential modes are shown in the tables below.

| Single-ended Input Voltage | Output Code (Offset binary format) |

|----------------------------|------------------------------------|

| +full scale                | FFFFh                              |

| zero                       | 00000h                             |

#### Single-ended Operation ADC Output Format

#### **Differential Operation ADC Output Format**

| Differential Input Voltage | Output Code<br>(Offset binary) | Output Code (two's complement) |

|----------------------------|--------------------------------|--------------------------------|

| +full scale                | FFFFh                          | 7FFFFh                         |

| zero                       | 80000h                         | 00000h                         |

| -full scale                | 00000h                         | 80000h                         |

#### SDADC20 Symbol and Pinout Table

| Pin Name | Туре         | Function                          |  |

|----------|--------------|-----------------------------------|--|

| AINP     | Analog Input | Positive analog input             |  |

| AINN     | Analog Input | Negative analog input             |  |

| VREFP    | Analog Input | Positive analog reference voltage |  |

| VREFN      | Analog Input   | Negative analog<br>reference voltage    | SDADC20                   |

|------------|----------------|-----------------------------------------|---------------------------|

| MODE       | Digital Input  | Single-ended or differential input mode | AINP AVSS                 |

| DGAIN[2:0] | Digital Input  | Digital Gain Select                     | DOUT[19:0]<br>—AINN       |

| AGAIN      | Digital Input  | Analog Gain Select                      | AGAIN<br>VREFP DGAIN[2:0] |

| DOUT[19:0] | Digital Output | ADC Digital Data                        | WREFN MODE                |

| AVSS       | Analog Power   | Ground reference                        |                           |

| AVDD       | Analog Power   | Analog power                            |                           |

### Performance Characteristics

| Parameter             | Description                  | Notes/Conditions                                                                                                                                                                                                                                                                                                                                                                                      | min                    | typ                                                                                                  | max                                   | units |

|-----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------|-------|

| ADC <sub>VHIGH</sub>  | Input voltage upper limit    |                                                                                                                                                                                                                                                                                                                                                                                                       |                        |                                                                                                      | VDD-<br>100mV                         | V     |

| ADC <sub>VLOW</sub>   | Input voltage lower limit    |                                                                                                                                                                                                                                                                                                                                                                                                       | AVSS+<br>100mV         |                                                                                                      |                                       | V     |

| ADC <sub>VRANGE</sub> | Input dynamic range          | Single-ended<br>Differential<br>(ADC <sub>VHIGH</sub> - ADC <sub>VLOW</sub> )                                                                                                                                                                                                                                                                                                                         | 0<br>-V <sub>REF</sub> |                                                                                                      | V <sub>ref</sub><br>+V <sub>ref</sub> | V     |

|                       | Common Mode Voltage<br>Range |                                                                                                                                                                                                                                                                                                                                                                                                       | AVSS+<br>100mV         | VDD/2                                                                                                | VDD-<br>100mV                         | V     |

| ADC <sub>RES</sub>    | Resolution                   | 60Hz Notch Mode<br>Resolution @ 10 sps<br>Resolution @ 20 sps<br>Resolution @ 40 sps<br>Resolution @ 80 sps<br>Resolution @ 160 sps<br>Resolution @ 320 sps<br>Resolution @ 640 sps<br>50Hz Notch Mode<br>Resolution @ 8.333 sps<br>Resolution @ 16.667 sps<br>Resolution @ 33.333 sps<br>Resolution @ 66.667 sps<br>Resolution @ 133.333 sps<br>Resolution @ 266.667 sps<br>Resolution @ 533.333 sps |                        | 20.0<br>19.0<br>18.0<br>16.0<br>13.0<br>11.0<br>20.0<br>19.0<br>19.0<br>18.0<br>16.0<br>13.0<br>11.0 |                                       | bits  |

| ADC <sub>DNL</sub>    | Differential nonlinearity    |                                                                                                                                                                                                                                                                                                                                                                                                       |                        |                                                                                                      | ±1                                    | LSB   |

| ADCINL              | Integral nonlinearity              | Uncalibrated                  |     |      | ±11 | LSB           |

|---------------------|------------------------------------|-------------------------------|-----|------|-----|---------------|

|                     | Zero Error after calibration       | ppm of full scale reference   | -10 |      | +10 | ppm<br>FSR    |

|                     | Zero Drift                         | zero code drift vs temp       |     | 50   |     | nV/°C         |

|                     | Full Scale Error after calibration | ppm of full scale reference   | -20 |      | +20 | ppm<br>FSR    |

|                     | Full Scale Error Drift             | full scale code drift vs temp |     | 0.05 |     | ppm<br>FSR/°C |

| ADC <sub>PSSR</sub> | Power Supply Rejection             |                               |     | TBD  |     | dB            |

| ADC <sub>CMR</sub>  | Common Mode Rejection              |                               |     | TBD  |     | dB            |

|                     | Normal Mode 50/60Hz<br>Rejection   |                               | 100 |      |     | dB            |

| G                   | Input Voltage Gain                 | Programmable                  | 1   |      | 128 |               |

|                     | Data Rate                          | Programmable                  | 2.5 | 10   | 400 | SPS           |

| $V_{REF}$           | Reference Voltage                  |                               | 1.8 | 2.5  | 3.2 | V             |

| V <sub>CMO_IN</sub> | Input Common Mode<br>Voltage       |                               | 100 | 2.5  | 4   | mV            |

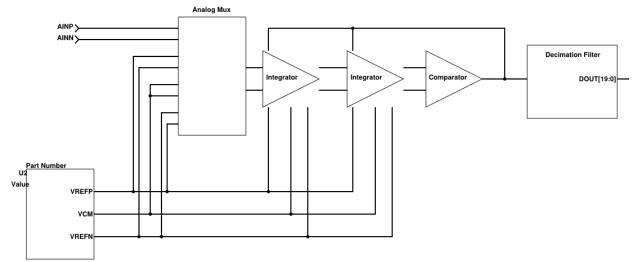

## SDADC20 Simplified Internal Circuit Schematic